It's been a while since I've attempted a new motor drive design, the last one being TinyCross's dual-motor 50V/100A drive about six years ago. I still really like that design, and those drives have worked well for TinyCross so far. But one of my favorite pastimes is looking for new components that might change how I would build something. And in the last six years, there's been an interesting development that I'm curious to explore: the GaNFET is now mainstream.

While they've been commercially available for a while, they're now both technically and economically viable as an alternative to silicon MOSFETs in certain power ranges, and have been adopted in many new consumer electronic devices. They are also becoming available in more conventional packages, though GaNFET purists would probably still use the bare-die versions for lowest parasitic inductance. Supporting components (mainly gate drivers), documentation, and device models are also now mature and widely available.

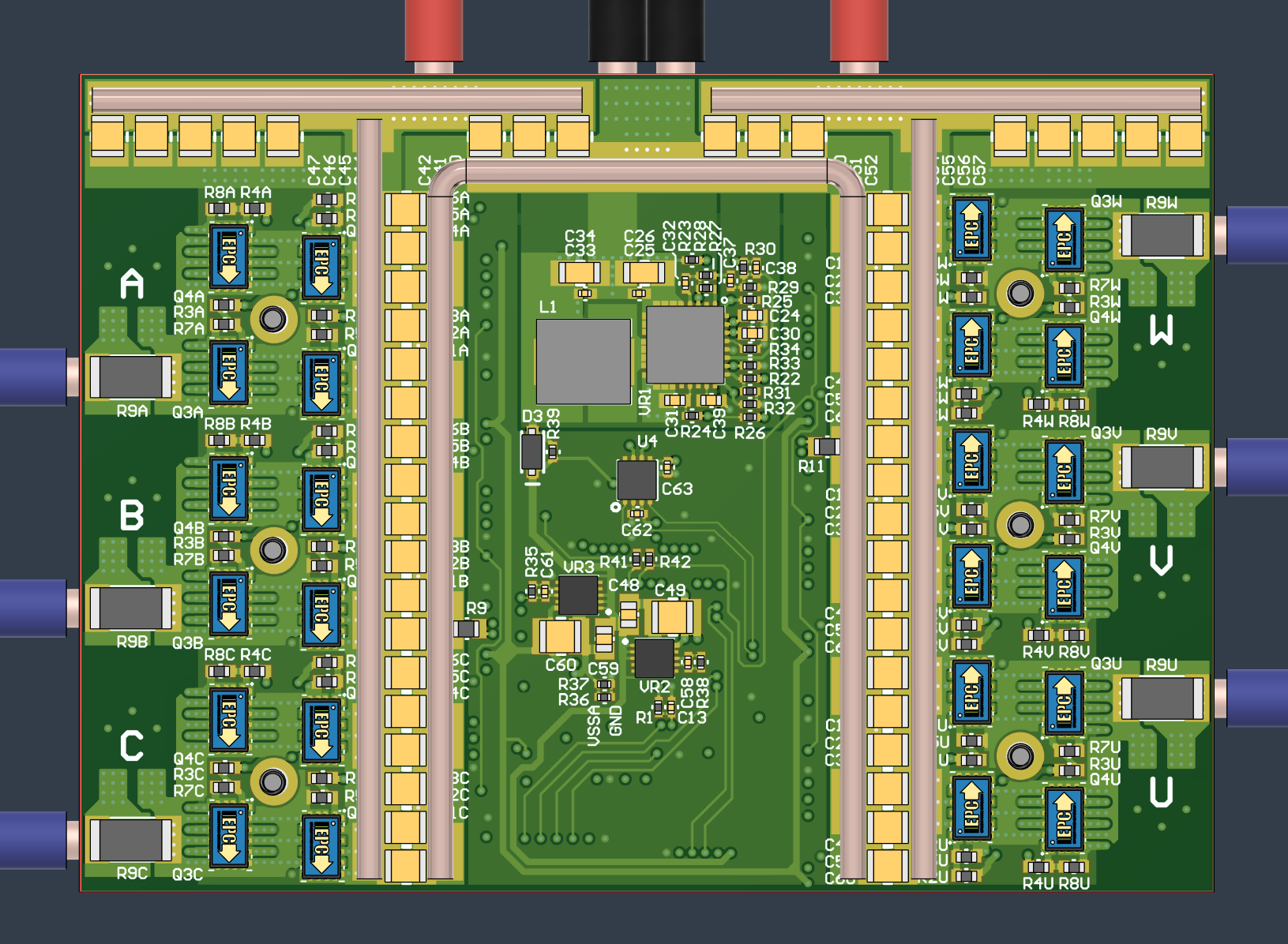

Of interest for this project are the EPC2302 and the brand new EPC2361 in 3x5 QFN. These are packaged GaNFETs, vs. the bare-die BGA and LGA options that have been around for a while. Ideally, encapsulating them in a thin plastic package improves robustness without sacrificing too much performance. The package also still exposes the die on the top side for direct cooling.

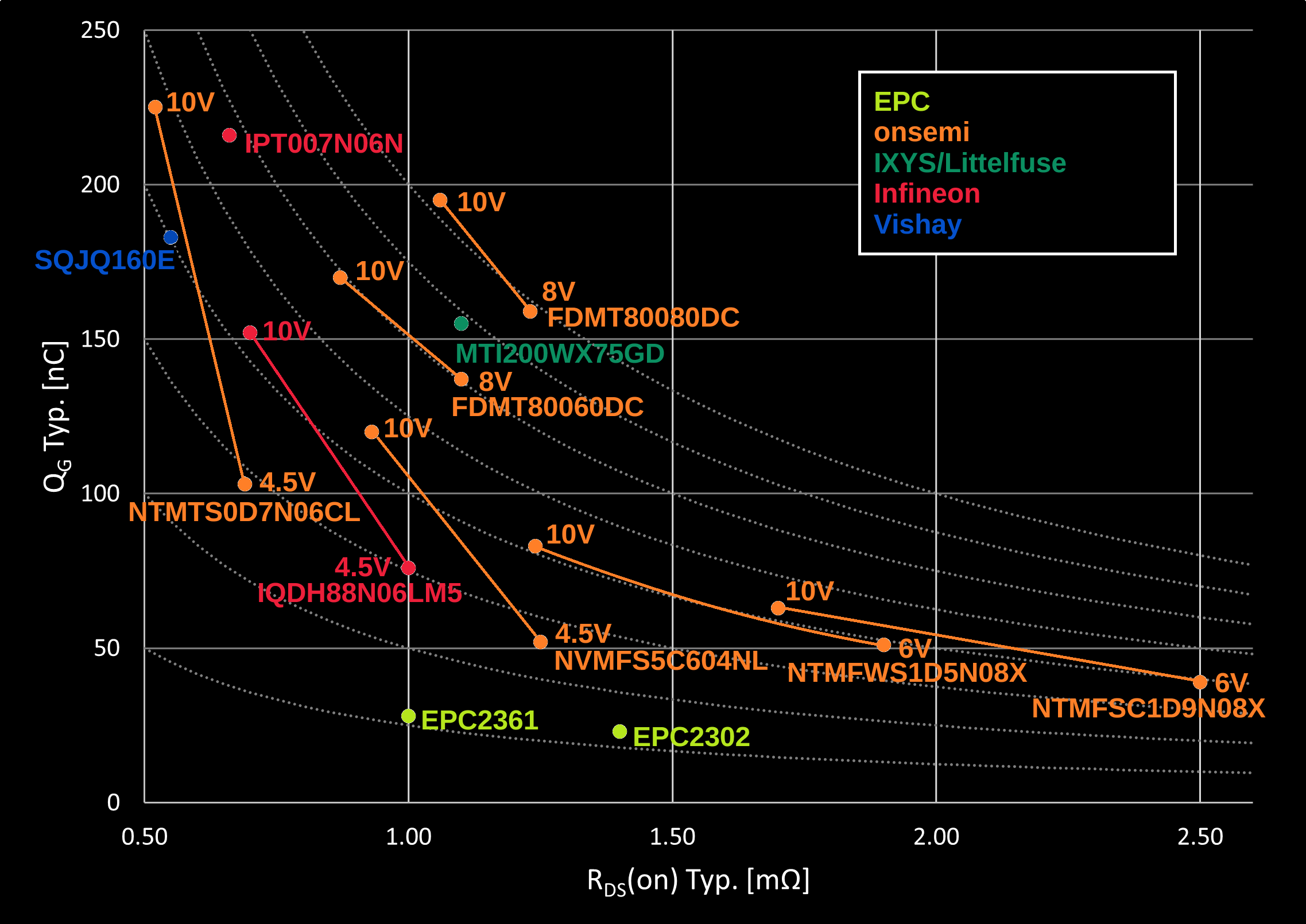

GaNFETs excel in the Figure-of-Merit (FoM) of on-resistance multiplied by gate charge, RDS(on)·QG, which captures both the conducting and switching losses. Here they are on a 2D plot with some silicon MOSFETs for comparison, with curves of constant FoM shown (lower is better):

The current TinyCross FETs, FDMT80080DC, can't really compete anymore. (I still love them for their pulsed current rating of 1453A, though.) The modern field of 60-80V silicon MOSFETs has significantly better FoM and also tends to publish specifications for lower gate drive voltages besides the standard 10V. The NVMFS5C604NL operated at VGS = 4.5V is especially remarkable. But the EPC GaNFETs still easily win on FoM, and they are 100V parts with half the surface area.

The extremely low QG means GaNFETs can be switched much faster than silicon MOSFETs. An EPC2302 half-bridge with a suitable layout and gate driver should have no problem operating at 100kHz PWM, or even higher. This reduces the need for large electrolytic capacitors on the DC bus, since the ripple current will be much lower. This is probably the largest contribution to space savings, even though the FETs themselves are also physically smaller.

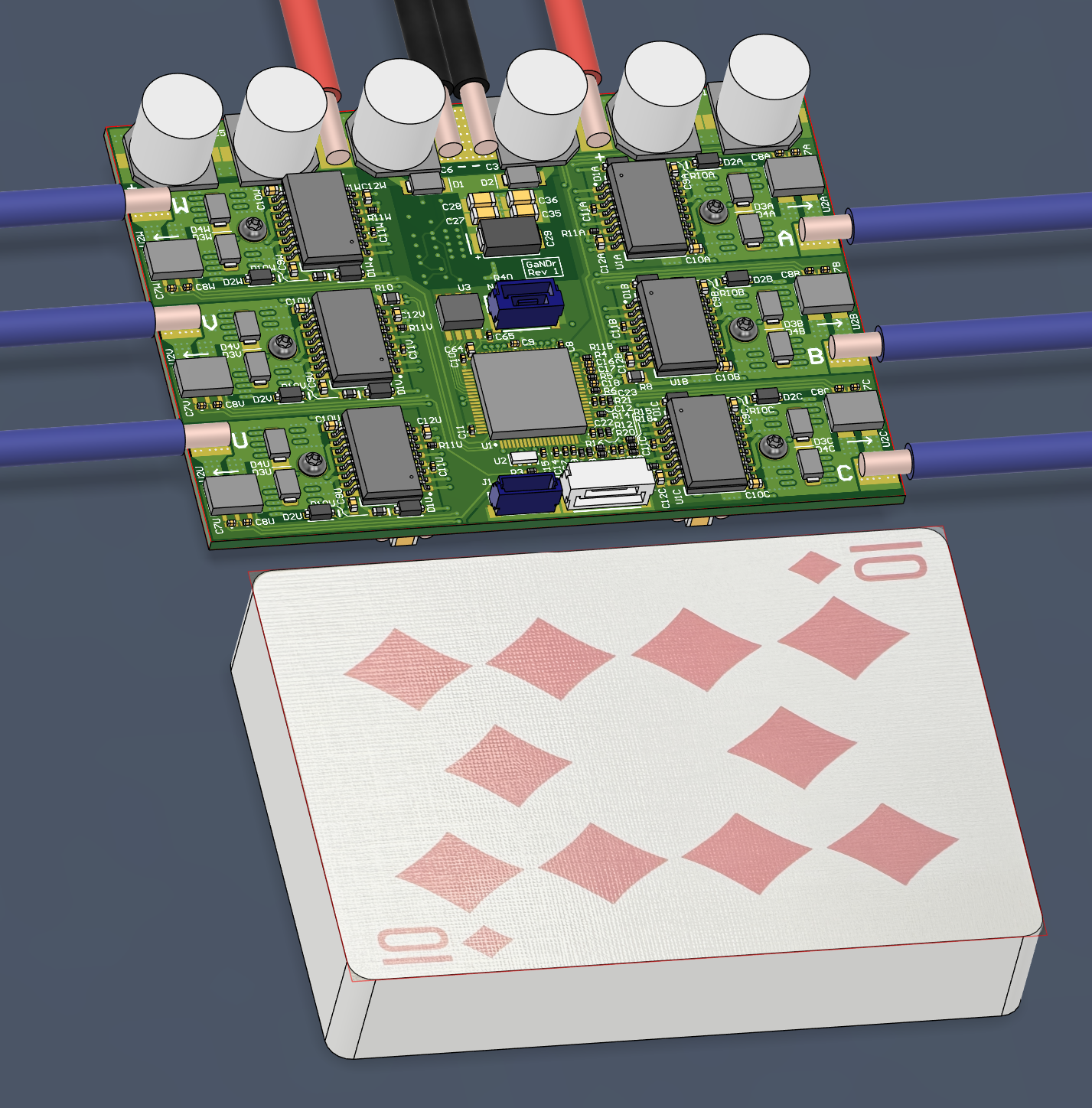

Although I'm not space-constrained on TinyCross, shrinking a power stage is always a fun project. I arbitrarily set a limit of the size of a deck of cards, with the same specification as the previous design (dual motor, 50V and 100A peak). Here's what the resulting layout looks like:

It's considerably smaller than the current TinyCross drive, even with the logic and power consolidated onto one board. There are half as many electrolytic capacitors, with more ceramic capacitors filling in at high frequencies. Optional 2mm bus bars help take some of the load off the PCB copper. The board can be mounted to a heat sink base with six isolated M2 screws located in the middle of each FET group for even mounting pressure. And the wires all exit horizontally, probably through grommets in the seam between the aluminum base and a 3D-printed cover.

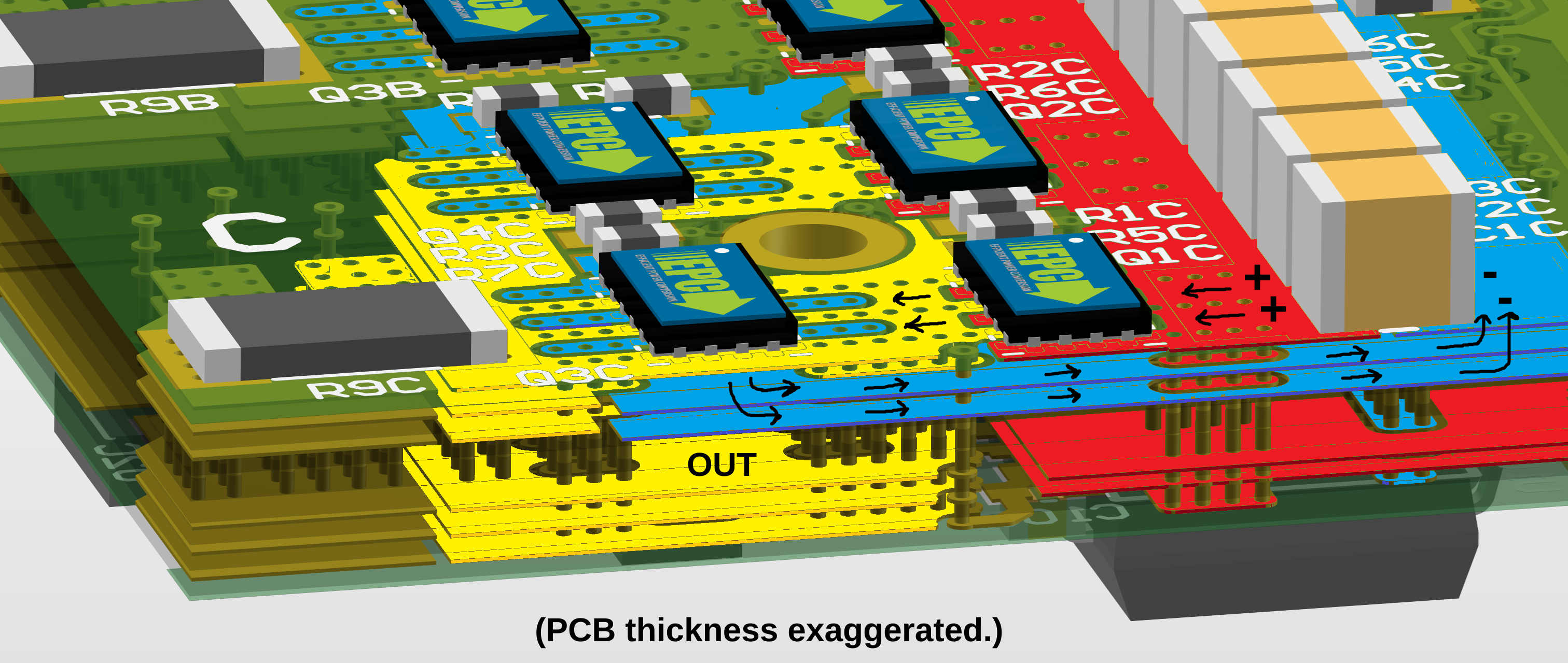

This is also a six-layer PCB, which further helps with layout. Six layer boards are now pretty fast and cheap thanks with JLCPCB, so there's not much reason to stick to four layers even for hobby motor drives anymore. The power stage layout follows EPC's recommended structure pretty closely, with the return path on the two inner layers closest to the FETs to minimize the dI/dt loop area:

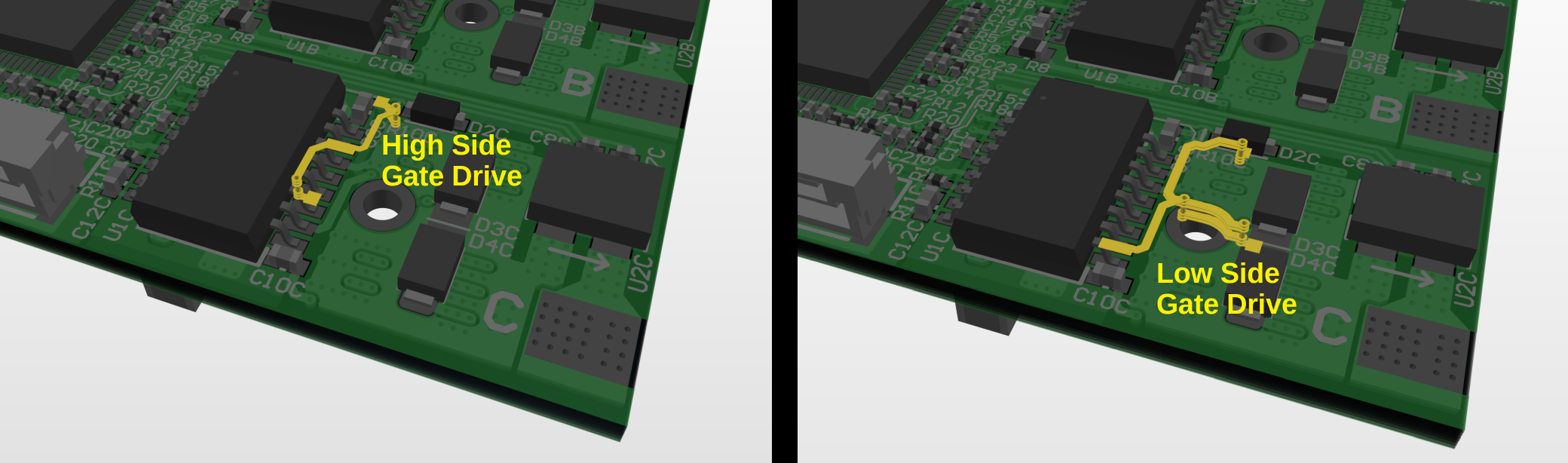

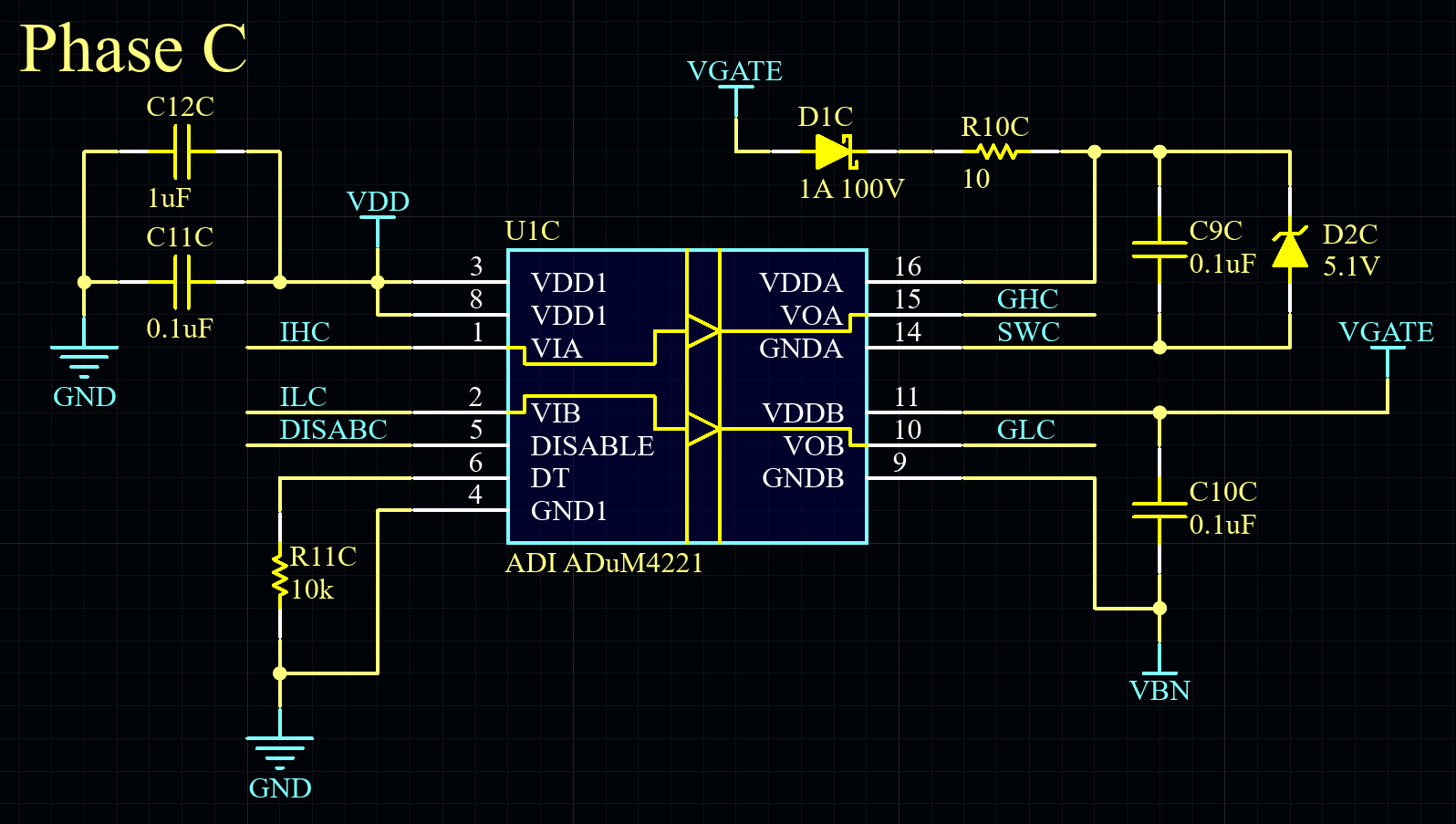

I did not follow the gate drive recommendations as strictly, since I need a lot of space for the gate drivers themselves. I am using isolated half-bridge drivers, and remarkably there are at least two pin-compatible parts from different manufacturers that could work. The Skyworks Si82E39x looks like the most promising option, with a 4V UVLO option and sub-10ns rise/fall times. It's not even that expensive, at around $4ea. The ADuM4221 from Analog Devices could also work, though. Although I have the driver on the opposite side of the board, I did try to keep the gate drive traces as short as possible:

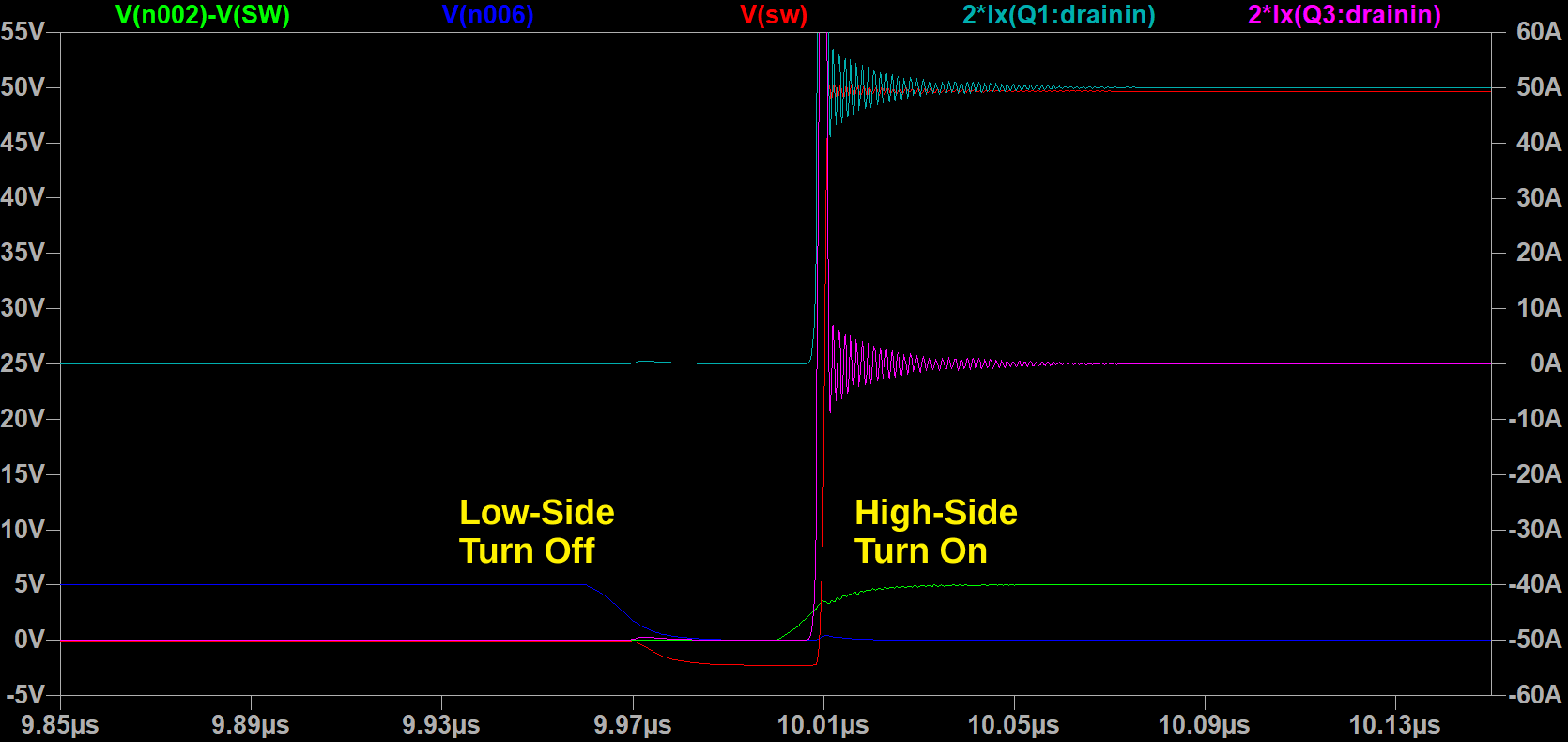

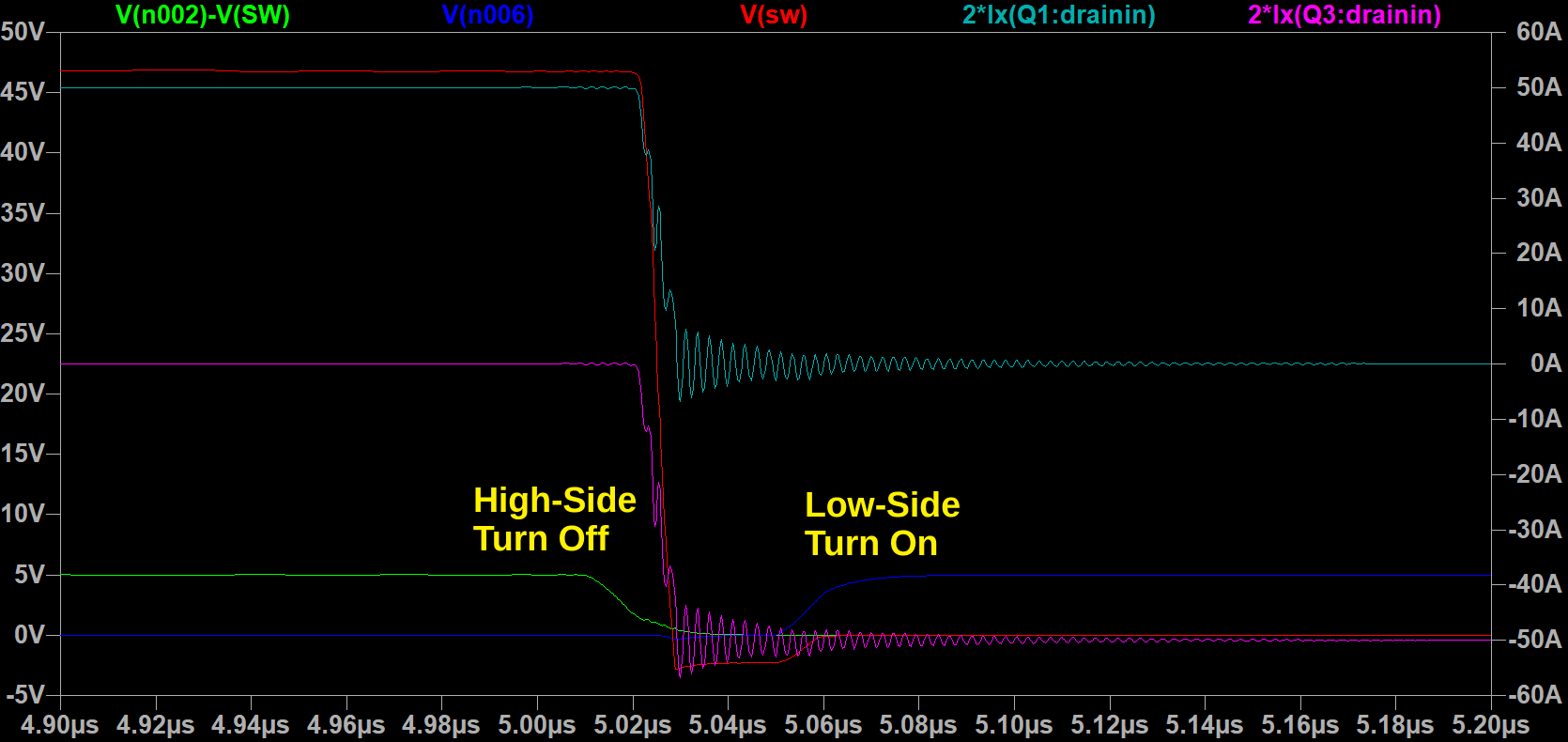

The gate drive return paths from the switch node (high-side) and negative plane (low-side) are also pretty direct. Will that be good enough? I don't really know - I don't have a 3D field solver. I'll have to wait for the boards. Ideally, with such low gate charge and fast drivers, it should be possible to run PWM frequencies above 100kHz and take the dead time down to around 50ns (less than 1%). Here's what the switching waveforms look like in an LTSpice simulation with the EPC device models:

However, this is just a guess for the loop inductance, so I won't really know how fast it can go until I get it on a scope. But what is the huge current spike on both FETs (shoot-through) during the high-side turn-on? I thought GaNFETs didn't have reverse recovery time? Well, I think it's just the Coss of the low-side FETs getting charged. Even though there's no body diode, there is still parasitic capacitance in the 1-2nF (per FET) range that has to get hard-switched at 50V. At these switching speeds, that requires a lot of current (for a very short period of time). If it turns out to be a problem, the gate drives will have to be artificially slowed down with extra gate resistance.

Another interesting quirk of GaNFETs is present in the LTSpice sim: during the deadtime, the low-side FETs do reverse-conduct, but at a voltage of around 2.25V, significantly higher than the body diode voltage across a silicon MOSFET. This partially eats into the power savings of a GaNFET design, but the more critical problem is what happens with a bootstrapped high-side driver. If the output is down at -2.25V, or even lower, even a crappy bootstrap diode won't drop enough from +5V to prevent the high-side VGS from exceeding 6V, the absolute maximum for these gates.

There are several ways to deal with this. Adding a resistor in series with the bootstrap diode creates low-pass filter with the bootstrap capacitor. A 10Ω resistor with a 0.1µF bootstrap capacitor has a time constant of 1µs, so a 50ns spike of +7V or so won't budge the voltage much. There is still a possibility that at very high duty cycle the average bootstrap charge voltage could exceed 6V, but I think you would run into other issues before that. For good measure, I also included a footprint for an optional 5.1V Zener diode across the bootstrap cap, which is another recommendation I saw.

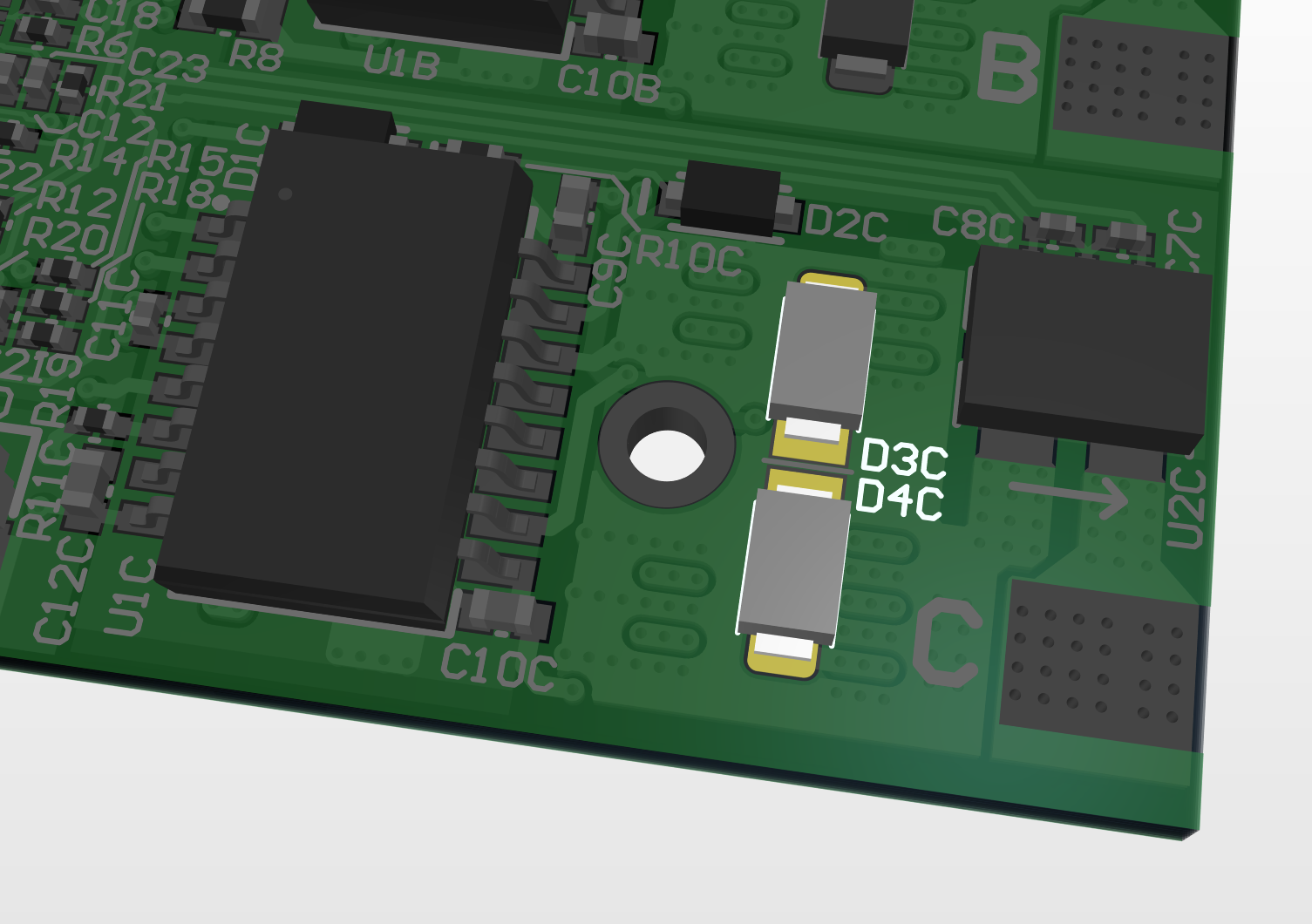

Lastly, I included a couple footprints for small Schottky diodes in parallel with the low-side FETs. I can only fit something like an SMA or SOD128 package, which max out at 5A for 100V devices. But some have pulse ratings at or above 100A, and these are very short pulses. At those pulse ratings the voltage drop is quite high, but still significantly below 2.25V. The other interesting question is whether the parasitic inductance of the diode and its connection to the bridge will prevent any of the high current from making it to them in the first place. Only the scope will tell.

In order to take advantage of the 100kHz+ low-deadtime PWM, I also want to try out another relatively new part, an MCU from the STM32G4 series. These are the spiritual successor to the F3 series that I've used for so many motor drives. They have lots of analog features, including five (!) ADC converters, DACs, op-amps, and comparators. But the G4 also adds several new peripherals that are specifically well-suited to motor drives:

The high-resolution timer (HRTIM) can drive up to 12 PWM outputs with a resolution as small as 184ps. It's probably overkill, but it allows for close to 16-bit duty cycle resolution at 100kHz, and very accurate deadtime control. For example, part-to-part variation in the gate driver propagation delays could probably be compensated There's also a CORDIC engine for offloading trigonometric functions from the CPU. And there's a Filter Math Accelerator (FMAC) peripheral, which includes a dedicated hardware multiplier/accumulator and memory for accelerating FIR/IIR filter calculations without involving the CPU.

The need for extra computation might make more sense if you've noticed what's missing from this design: there are no inputs for motor position sensing. While I love the simplicity and robustness of TinyCross's optically-isolated virtual Hall sensors, it's nothing interesting in terms of brushless motor control. I did manage to run two instances of a lightweight flux observer in the background on the F3, but I never used it for driving the current control. I'm sure it would have worked at speed, but the main problem with sensorless control for TinyCross is getting starting torque on all four drive motors without them fighting each other.

One way to get the position of the motor before the flux observer converges is with High-Frequency Injection (HFI). The motors on TinyCross have an L/R time constant of around 1.5ms, so at frequencies above 1kHz they are mostly inductors. The inductance on each phase varies depending on the position of the rotor, since the permanent magnet flux changes where each phase's stator steel is on a non-linear B-H curve. That inductance change can be measured with a high-frequency signal on top of the normal drive voltage to derive the position. This is nothing new - it's been basically perfected in VESC - but it should be fun to try to implement with 100kHz+ PWM and the STM32G4's extra processing power.

That's it for now - more to come when there is physical hardware to look at.